What is time borrowing: Latches exhibit the property of being transparent when clock is asserted to a required value. In sequential designs, using latches can enhance performace of the design. This is possible due to time borrowing property of latches. We can define time borrowing in latches as follows:

Time borrowing is the property of a latch by virtue of which a path ending at a latch can borrow time from the next path in pipeline such that the overall time of the two paths remains the same. The time borrowed by the latch from next stage in pipeline is, then, subtracted from the next path's time.

The time borrowing property of latches is due to the fact that latches are level sensitive; hence, they can capture data over a range of times than at a single time, the entire duration of time over which they are transparent. If they capture data when they are transparent, the same point of time can launch the data for the next stage (of course, there is combinational delay from data pin of latch to output pin of latch).

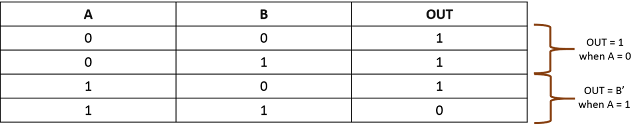

Let us consider an example wherein a negative latch is placed between two positive edge-triggered registers for simplicity and ease of understanding. The schematic diagram for the same is shown in figure 1 below:

|

| Figure 1: Negative level-sensitive latch between two positive edge-triggered registers |

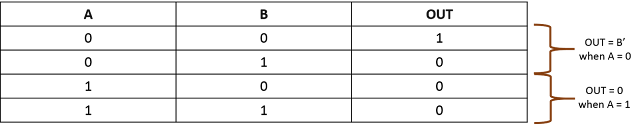

Figure 2 below shows the clock waveform for all the three elements involved. We have labeled the clock edges for convenience. As is shown, latB is transparent during low phase of the clock. RegA and RegC (positive edge-triggered registers) can capture/launch data only at positive edge of clock; i.e., at Edge1, Edge3 or Edge5. LatB, on other hand, can capture and launch data at any instant of time between Edge2 and Edge3 or Edge4 and Edge5.

|

| Figure 2: Clock waveforms |

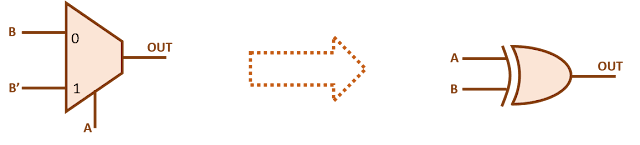

The time instant at which data is launched from LatB depends upon the time at which data launched from RegA has become stable at the input of latB. If the data launched at Edge1 from RegA gets stable before Edge2, it will get captured at Edge2 itself. However, if the data is not able to get stable, even then, it will get captured. This time, as soon as the data gets stable, it will get captured. The latest instant of time this can happen is the latch closing edge (Edge3 here). One point here to be noted is that at whatever point data launches from LatB, it has to get captured at RegC at edge3. The more time latch takes to capture the data, it gets subtracted from the next path. The worst case setup check at latB is at edge2. However, latch can borrow time as needed. The maximum time borrowed, ideally, can be upto Edge3. Figure 3 below shows the setup and hold checks with and without time borrow for this case:

|

| Figure 3: Setup check with and without time borrow |

The above example consisted of a negative level-sensitive latch. Similarly, a positive level-sensitive latch will also borrow time from the next stage, just the polarities will be different.

Also read:

Also read: