Those timing paths, which are very hard to meet in timing are called timing critical paths. They can be divided into setup and hold timing critical paths.

Inherent frequency limit and delay variations: Let us say, we want our chip to remain functional within following PVTs:

For a setup slack of 0 ps, operating clock frequency will be maximum; i.e.,

Also read:

Setup timing critical paths: Those paths for which meeting setup timing is difficult, can be termed as setup critical timing paths. For these paths, the setup slack value is very close to zero and for the most part of design cycle, remains below zero.

Hold timing critical paths: As is quite obvious, those paths for which meeting hold timing is difficult, are hold critical paths. These paths may require many buffers to meet hold slack equation.

Sometimes, we may encounter some timing paths which are violating in both setup and hold. There is not enough setup slack to make them hold timing clean and vice-versa. The good practice in timing analysis is to identify all such paths as early as possible in design cycle. Let us discuss the scenarios that make timing paths both setup and hold timing critical.

Inherent frequency limit and delay variations: Let us say, we want our chip to remain functional within following PVTs:

Process : Best-case to Worst-case

Voltage : 1.2 V with 10% voltage variation allowed (1.08 V to 1.32 V)

Temperature : -20 degrees to+150 degress

The delay of a standard cell changes with PVTs and OCVs. Let us only talk about PVT variations. Let us say, cell delay changes by 2 times from worst case scenario (worst process, lowest voltage, worst temperature) to best case scenario (best process, highest voltage, best temperature). Let us say, setup and hold checks also scale by same amount. Remember that the equations for setup and hold need to be satisfied across all the PVTs. Which essentially means setup needs to be ensured for WCS scenario and hold timing needs to be ensured for BCS scenario. This will provide a limit to maximum frequency that the path can be timed at. If we try to go beyond that frequency, we will not be able to ensure both setup and hold slacks remain positive.

Let us illustrate with the help of an example of a timing path from a positive edge-triggered flip-flop to positive edge-triggered flip-flop with a frequency target of 1.4 GHz (clock time period = 714 ps). Let us say, we have the Best-case and Worst-case scenarios as shown in figure 1 and 2.

Figure 1 shows that the best-case clk->q delay for launch flop is 100 ps, best-case combinational delay is 80 ps and best-case hold time is 200 ps. Applying our hold timing equation for this case,

Hold slack = Tck->q + Tprop - Thold

Hold slack = 100 + 80 - 200

Hold slack = -20 ps

So, in this case, our hold slack comes out to be negative. So, we need to apply the techniques to improve our hold slack. But we need to ensure that our setup slack is sufficiently positive. Let us look at the worst-case scenario to know about our setup slack. If we assume that everything scales by 2 times, the worst-case numbers for clk->q delay, combinational delay and setup/hold time come out to be 200 ps, 160 ps and 400 ps respectively.

Applying setup timing equation for this scenario,

Setup slack = Tperiod - (Tck->q + Tprop + Tsetup)

Setup slack = 714 - 200 - 160 - 400 = -36 ps

Thus, for the same timing path, both setup and hold slacks are coming out to be negative. For this path, we cannot meet both setup and hold provided all these conditions. One of the solutions could be to use cells with less delay variability. Or we can limit the operating conditions to a tighter range, for instance, 1.15 to 1.25 V instead. This will improve both setup and hold slack values. If this is not an option, the only option left to satisfy timing is to add delay elements to bring hold slack to zero and reduce the frequency as the inherent variations of cells will not allow the path to operate beyond a certain frequency. Let us check at what maximum frequency our timing path will work.

First, we need to ensure hold timing is met. Thus,

Hold slack >= 0This translates to Combinational delay (Cb) > 100 ps, or Cb = 100 ps for a hold slack of 0 ps. In other words, worst case combinational delay is 200 ps (2 times scaling).

For a setup slack of 0 ps, operating clock frequency will be maximum; i.e.,

Tperiod(min) = Tck->q + Tprop + Tsetup

Tperiod(min) = 200+ 200 + 400 = 800 psThe minimum time period that it can operate at is 800 ps, or a maximum frequency of 1.25 GHz.

In this post, we have discussed how PVT variations in delay can cause a timing path to be both setup and hold critical. Also, we discussed how it limits the frequency of operation. Although the discussion was limited to only PVT variations, OCV variations will add to the variations. The inherent equations will certainly remain same though. Also, we did not take an important parameter into consideration; i.e. clock skew. Can you think of how clock skew between the two flip-flops contribute to maximum achievable clock frequency? Or is it unrelated to clock skew?

Also read:

- Setup and hold checks

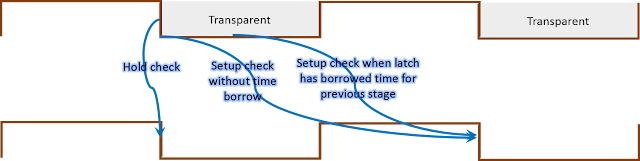

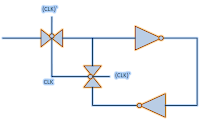

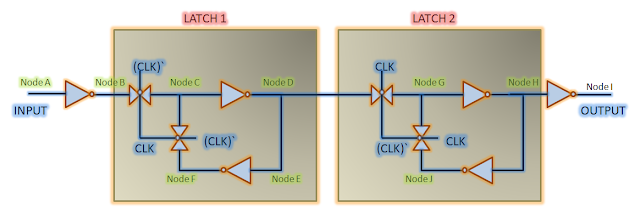

- Basics of latch timing

- Modeling skew requirements with setup and hold checks

- False paths basics and examples