Problem: Suppose there are 'N' signals which are to be skew matched within a window of 200 ps with respect to each other. Model this requirement with the help of data setup and hold checks.

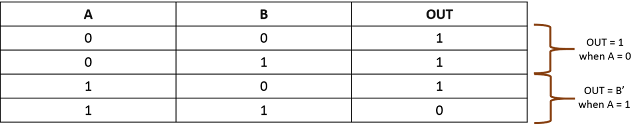

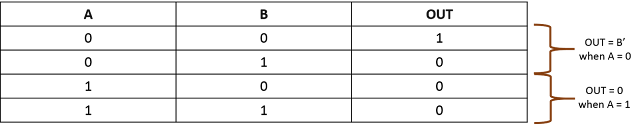

As we discussed in data setup and data hold checks, data setup check of 200 ps means that constrained data should come at least 200 ps before the reference data. Similarly, data hold check of 200 ps constrains the constrained data to come at least 200 ps after the reference data. The same is shown pictorially in figure 1(a) and 1(b).

|

| Figure 1(a): Data setup check of 200 ps constrains the constrained signal to toggle at-least 200 ps before reference signal toggles. |

|

| Figure 1(b): Data hold check of 200 ps constrains the constrained signal to toggle at-least 200 ps after the reference signal has toggled. |

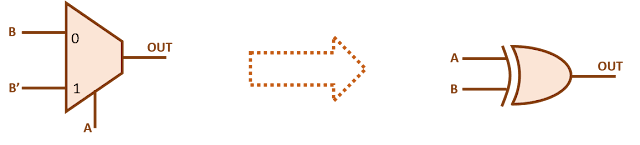

Now, suppose you apply a data setup check of -200 ps instead of 200 ps. This would mean that the constrained signal can toggle upto 200 ps after the reference signal. Similarly, a data hold check of -200 ps would mean that the constrained signal can toggle from 200 ps before the reference signal. If we apply both the checks together, it would infer that constrained signal can toggle in a window that ranges from 200 ps before the toggling of reference signal to 200 ps after the toggling of reference signal. This is pictorially shown in figures 2(a) and 2(b).

|

| Figure 2(a): Negative data setup and hold checks of 200 ps |

If we combine the two checks, it implies that the constrained data can toggle upto 200 ps after and from 200 ps before the reference signal. In other words, we have constrained the constrained signal to toggle in a window +- 200 ps within the reference signal.

Coming to the given problem, if there are a number of signals required to toggle within a window of 200 ps, we can consider one of these to act as reference signal and other signals as constrained signals. The other signals can then be constrained in both setup and hold with respect to reference signal such that all of these lie within +-100 ps of the reference signal. The same is shown in figure 3 below:

|

| Figure 3: Data checks to maintain skew between N signals |